# PhD in Electronic Engineering PhD Cycle XXXV

# Design and Implementation of 100+ Gbps Packet Processing Accelerators

Marco Spaziani Brunella

A.Y. 2022/2023

Tutor: Prof. G. Bianchi

Coordinator: Prof. C. Di Natale

#### Abstract

One of the most disruptive ideas in computer network design is the introduction of Software-Defined Networking (SDN) and Network Function Virtualization (NFV). At the idea's core is the willingness to enhance the programmability of high-speed network devices without sacrificing performance. SDN and NFV are pure software approaches, relying on the underlying general-purpose (e.g., x86 CPUs) hardware to execute efficiently. General purpose computing infrastructure has been showing a consistent decline in performance growth over the last decade, providing diminishing returns at each new generation of devices. With 100gbps widely deployed in hyperscalers infrastructure, a software approach is no longer an option.

This dissertation aims to rethink packet processing architectures from the ground up by designing and implementing Domain-Specific hardware architectures to process line-rate traffic at 100+ Gbps. In particular, this work examines the requirements for line-rate processing and languages to describe packet processing tasks, proposing a Very-Long Instruction Word (VLIW) processor called Sephirot, able to execute native extended Berkeley Packet Filter (eBPF) code. Furthermore, the VLIW core is complemented by a set of Maps and Helper Functions, constituting a complete network processing offload system called hXDP. This system is then implemented on a NetFPGA-SUME and tested against an x86 CPU with a set of microbenchmarks and real-world use cases, such as Meta's Load Balancer Katran. Finally, I propose a TCAM-based engine called Program Warping as a frontend to hXDP to accelerate the packet parsing portion of every network program. This engine can dramatically reduce the number of instructions needed to process a packet to the extent of a 1-clock cycle decision on specific paths of Suricata, an open-source Intrusion Detection System (IDS).

#### Acknowledgements

First, I would like to thank my advisor, Prof. Giuseppe Bianchi, for all the feedback and guidance during and before my Ph.D. journey began. I sincerely thank Marco Bonola, with whom I have been working on this fantastic and long journey, for his passion and expertise in the field. A special thanks go to Roberto Bifulco from NEC Laboratories Europe, who mentored me throughout my Ph.D. journey and immensely contributed to the person I am today. Last but not least, I wanted to thank my partner Giulia for never letting me miss my true north.

# Contents

| 1                          | Intr | troduction                                                       |    |  |

|----------------------------|------|------------------------------------------------------------------|----|--|

|                            | 1.1  | Background and Motivations                                       | 2  |  |

|                            | 1.2  | Strategy, Vision and List of Contributions                       | 4  |  |

|                            | 1.3  | State of the Art                                                 | 8  |  |

|                            | 1.4  | Structure of the Dissertation                                    | 9  |  |

|                            |      | 1.4.1 List of Published Material                                 | 10 |  |

| 2                          | Mo   | dern Networks Overview                                           | 13 |  |

|                            | 2.1  | Software-Defined Networking                                      | 13 |  |

|                            |      | 2.1.1 The OpenFlow Protocol                                      | 15 |  |

|                            | 2.2  | Network Function Virtualization                                  | 15 |  |

| 2.3 Berkeley Packet Filter |      | Berkeley Packet Filter                                           | 17 |  |

|                            |      | 2.3.1 eBPF Virtual Machine                                       | 19 |  |

|                            |      | 2.3.2 eBPF Instruction Set Architecture                          | 20 |  |

|                            |      | 2.3.3 Maps                                                       | 25 |  |

|                            |      | 2.3.4 Helper Functions                                           | 25 |  |

|                            | 2.4  | eXpress Data Path                                                | 26 |  |

| 3                          | Sep  | hirot: a Very-Long Instruction Word Processor for Networking Ap- |    |  |

|                            | plic | ations                                                           | 27 |  |

CONTENTS 5

|   | 3.1 | Sephir | ot architecture                            | 30 |

|---|-----|--------|--------------------------------------------|----|

|   | 3.2 | Synthe | esis Results                               | 35 |

|   |     | 3.2.1  | Full-core Synthesis                        | 36 |

|   | 3.3 | Perfor | mance-Area Tradeoff                        | 41 |

|   |     | 3.3.1  | ILP Analysis                               | 41 |

|   |     | 3.3.2  | 2 Lanes Implementation                     | 49 |

|   |     | 3.3.3  | 4 Lanes - Half Memory Unit Implementation  | 51 |

| 4 | hXI | OP: So | oftware Packet Processing on FPGA NICs     | 55 |

|   | 4.1 | Challe | enges                                      | 56 |

|   | 4.2 | hXDP   | Overview                                   | 57 |

|   | 4.3 | Hardw  | vare Architecture                          | 58 |

|   |     | 4.3.1  | Architecture and components                | 58 |

|   |     | 4.3.2  | Pipeline Optimizations                     | 60 |

|   |     | 4.3.3  | Implementation                             | 61 |

|   | 4.4 | Comp   | ile-Time Optimizations                     | 62 |

|   | 4.5 | Evalua | ation                                      | 65 |

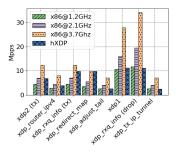

|   |     | 4.5.1  | Test Results                               | 66 |

|   |     | 4.5.2  | Comparison to other FPGA solutions         | 70 |

|   |     | 4.5.3  | Discussion                                 | 71 |

| 5 | Pro | gram ` | Warping: Faster Hardware Packet Processing | 72 |

|   | 5.1 | Requi  | rements and Challenges                     | 75 |

|   | 5.2 | System | n Design                                   | 76 |

|   |     | 5.2.1  | Warp Optimizer                             | 78 |

|   |     | 5.2.2  | Program analysis                           | 79 |

|   |     | 5.2.3  | Match-action rules generation              | 80 |

|   |     | 5.2.4  | Warp Engine                                | 83 |

CONTENTS 6

| 6 | Cor | nclusio | ns 10°                            | 1 |

|---|-----|---------|-----------------------------------|---|

|   | 5.4 | Discus  | ssion                             | 8 |

|   |     | 5.3.5   | End-to-end performance            | 6 |

|   |     | 5.3.4   | Warp Engine Hardware Requirements | 5 |

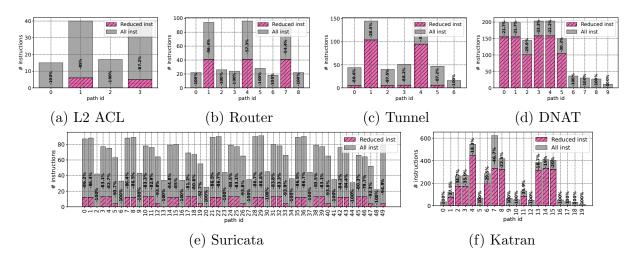

|   |     | 5.3.3   | Warped instructions               | 2 |

|   |     | 5.3.2   | Functional Equivalence            | 2 |

|   |     | 5.3.1   | Applications                      | 9 |

|   | 5.3 | Evalua  | ation                             | 9 |

|   |     | 5.2.9   | Implementation                    | 7 |

|   |     | 5.2.8   | Integration with hXDP             | 6 |

|   |     | 5.2.7   | Context Restoration Unit          | 5 |

|   |     | 5.2.6   | Match-action Unit                 | 5 |

|   |     | 5.2.5   | Key Extractor                     | 4 |

# Chapter 1

# Introduction

Today, everything runs through the Internet, the largest network of devices. In the last couple of decades, this Network Infrastructure has become one of the critical backbones of our society. In this timeframe, this infrastructure needed to be always more capable of offering new and complex services, such as proxies, caches, routing, and firewalls. As a network operator, the ability to reconfigure and adapt the existing devices composing the network has become a must-have feature.

Given the flexibility of modern networks and the need to continuously support new applications, operators have turned to pure software implementations for such functions, using a mix of well-defined approaches: Software Defined Networks (SDN) and Network Function Virtualization (NFV). The goal of SDN is to logically separate the network control functions from the network forwarding functions, while NFV seeks to abstract network functions from the underlying hardware. The natural consequence of this solution is that servers in operator networks spend a significant fraction of their CPU's resources to process network traffic coming from their network interface cards (NICs).

A pure CPU-based approach has already started to provide diminishing returns. Modern CPUs must be faster to cope with 100+Gbps network traffic streaming in from the NIC without severely compromising peak throughput and latency, which are essential

elements of current workloads such as Virtual/Augmented Reality, the Metaverse, and live event streaming.

For the reasons mentioned above, modern network operators must challenge those paradigms and deploy new architectures to overcome the limitations of running networks on top of a general-purpose infrastructure. In the rest of this chapter, we will analyze and discuss the motivations beyond these challenges. We will then present the contributions of this Dissertation to the state of art. This chapter partially includes figures and verbatim copies of the text of my first-author papers.

#### 1.1 Background and Motivations

Modern networks are called to efficiently and flexibly support an ever-growing variety of heterogeneous middlebox-type functions such as network address translation, tunneling, load balancing, traffic engineering, monitoring, intrusion detection, and so on. This flexibility, combined with the increasing demands in packet processing throughput, is hugely challenging. While a network's speed increases, it decreases the time budget to perform meaningful transformations to the data. Network speed has increased by 100x in the last decade. In contrast, CPUs processing this data stream has yet to match such a growth, mainly due to two reasons: the first one is related to the CMOS technology at the heart of every CPU and the other one is related to every program running on a CPU-based system.

End of Dennard's scaling Law. Dennard's scaling law can be reduced to: "as transistors become smaller, they become cheaper, faster and consume less power." This observation mainly drove the ability to cram more transistors inside a chip that, as transistors become smaller, they become faster, consume less power, and become easier to manufacture.

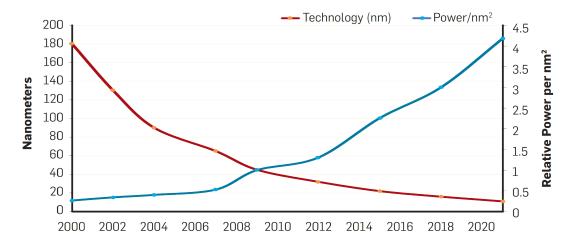

This observation started to shake in the last couple of decades, as shown in Fig. 1.1

, as transistors became smaller, their energy density ramped up, eventually leading to sophisticated power management techniques and limiting the maximum frequency at which a chip can run.

Figure 1.1: Transistor Scaling trends of Supply Voltage and Power Density

In fact, the powerd drawn by the supply of a CMOS chip is given by the following equation:

$$P_{dynamic} \propto \frac{1}{2} \times V_{DD}^2 \times f_{CLK}$$

The critical limit of the technology is thus the power density of the die. The industry has reduced the dynamic power by lowering  $V_{DD}$ . Still, we are now in a situation where no further decrease can be successfully achieved without violating the noise margins of the design. Moreover, we don't want to decrease the  $f_{CLK}$  since it's directly related to how many instructions we can execute in a single cycle. Thus, around the beginning of the 2000s, the so-called power wall was hit, pinning the clock frequency for desktop CPUs at  $\sim 3-4GHz$ .

Amdhal's Law If we take any program running on a CPU, it will be composed of a stream of logical instructions executed one after the other. Modern CPU architectures typically employ deep pipeline stages and multiple execution units (e.g., superscalar

processors) to increase the number of instructions churned per clock cycle, increasing the Instructions Per Cycle (IPC). On a higher abstraction level, modern workloads are divided into threads that can be executed independently on the different cores of a many-core CPU.

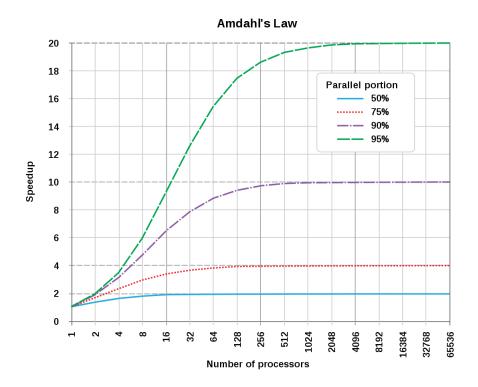

Leveraging Instruction Level Parallelism (ILP) and Thread Level Parallelism (TLP) helped us to offset the need for better single-thread performance of the CPUs, ultimately bottlenecked by the end of Dennard's scaling law. ILP and TLP are metrics that heavily depend on the kind of workload we're running. More specifically, they rely on the amount of concurrency we can extract from the workload. The speedup we gain by parallelizing a portion x of a workload W is given by Amdahl's law:

$$speedup = \frac{1}{(1 - W) + \frac{W}{x}}$$

Plotting the equation mentioned above in **Fig. 1.2**, we can see that it doesn't make sense to deploy hundreds or thousands of cores on workloads that exhibit poor concurrency characteristics, which is the case of network processing tasks.

#### 1.2 Strategy, Vision and List of Contributions

This dissertation aims to provide a more general and easy-to-use solution to program packet processing on Field-Programmable Gate Arrays (FPGAs) Netowrk Interface Cards (NICs), using little FPGA resources while seamlessly integrating with existing operating systems. Computers in datacenter and telecom operator networks employ a significant fraction of their CPU's resources to process network traffic coming from their NICs. Enforcing security, for example, using a firewall function, monitoring network-level performance, and routing packets toward their intended destinations, are just a few examples of the tasks being performed by these systems. With NIC's port speeds growing beyond 100Gigabit/s (Gbps), and given the limitations in further scaling CPUs performance, new hardware

Figure 1.2: Diminishing returns as we increase the number of execution units given a fixed amount of intrinsic concurrency

architectures need to be introduced to handle these growing workloads.

From an OS interface perspective, this dissertation explores using the extended Berkeley Packet Filter (eBPF) [3] as a Domain-Specific Language to describe packet processing tasks. eBPF is a technology that enables running of small programs within the Linux kernel in a sandboxed environment, the eBPF virtual machine (VM). The eBPF VM has its Instruction Set Architecture (ISA), which implements a register architecture with a program counter (PC) register, 10 general purpose registers (R0 - R9), and a read-only stack pointer register (R10) that contains the address of a 512B memory area used as program's stack. The registers and the stack capture the current program's state, which resets every time a new run is triggered. To save state across program runs, eBPF pro-

vides unique data structures called maps. These are memory areas defined at compile time and organized as lookup tables. eBPF programs are usually written in a high-level language, such as C, and compiled to the eBPF bytecode that uses the eBPF Instruction Set Architecture (ISA). The eBPF bytecode can be loaded in the kernel using different hooks. Depending on the hook, the program execution triggers changes, and so does the eBPF input data structure. For instance, in this dissertation, we focus on the XDP hook, and call XDP programs an eBPF program attached to the XDP hook. The hook is provided at the NIC driver level. Whenever a packet is received, the XDP environment: (i) creates an xdp\_md struct to contain the packet buffer pointers and metadata, such as the packet's input port id; (ii) sets R0 to point to the address of the memory area hosting the struct; (iii) and then starts the VM to run the XDP program. At the end of its execution, the program can return a forwarding decision for the packet by writing in R0 one of the following four values: (i) XDP\_DROP, to drop it; (ii) XDP\_PASS, to pass the packet to the next level in the network stack; (iii) XDP\_TX, to transmit the packet to the same port it was received on; (iv) XDP\_REDIRECT, to transmit the packet to a different port.

From a hardware architecture standpoint, this dissertation explores three hardware architectures, each building on top of the other, to achieve line-rate throughput with sub-microsecond latency. Sephirot is a VLIW processor with four parallel lanes that execute eBPF instructions. Sephirot is designed as a pipeline of four stages: instruction fetch (IF); instruction decode (ID); instruction execute (IE); and commit. A program is stored in a dedicated instruction memory, from which Sephirot fetches the instructions in order. The processor has another dedicated memory area to implement the program's stack, which is 512B in size, and 11 64b registers are stored in the register file. These memory and register locations match one-to-one the abovementioned eBPF virtual machine specification. We perform a design-space exploration of Sephirot growing and shrinking the number of parallel lanes, evaluating the amount of Instruction Level Parallelism (ILP)

we can extract from network packet processing workloads. We then synthesize the various design onto a NetFPGA-SUME [67].

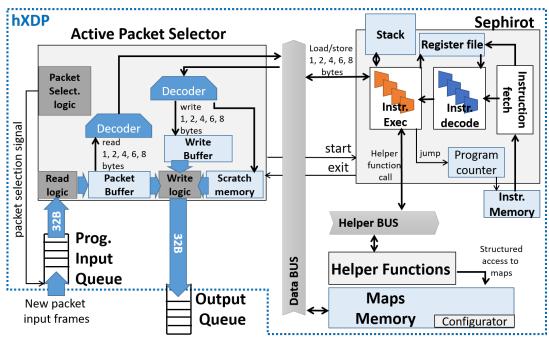

hXDP is an entire eBPF runtime execution system on FPGA. It's built on top of Sephirot and features the minimum set of *Maps* and *Helper Functions* needed to support native eBPF/XDP program execution. To evaluate hXDP, we provide an open-source implementation for the NetFPGA. We tested our implementation using the XDP example programs provided by the Linux source code and using two real-world applications: a simple stateful firewall and Facebook's Katran load balancer. hXDP can match the packet forwarding throughput of a multi-GHz server CPU core while providing a 10x lower forwarding latency. This is achieved despite the low clock frequency of our prototype (156MHz) and using less than 15% of the FPGA resources.

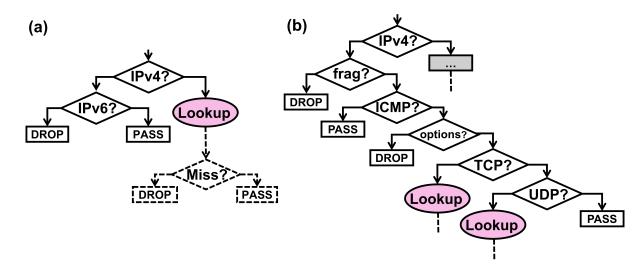

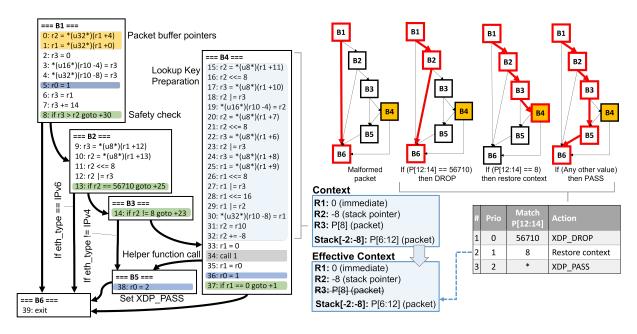

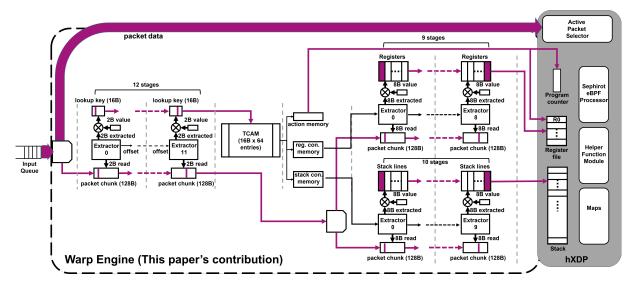

Program Warping builds on the observation that a subset of the eBPF/XDP program's instructions implements typical packet processing tasks, such as packet header parsing, which can be efficiently implemented in architectures with a high degree of pipeline-level parallelism [13, 18]. Therefore, under the constraint of keeping transparency to the programmer, we address two main issues in our design: (i) identifying, from the eBPF bytecode, the tasks that can be efficiently parallelized; (ii) designing an FPGA pipeline that runs such tasks leveraging their parallelism, while providing runtime reconfigurability and using minimal hardware resources. We address the two issues extending technologies that run eBPF programs on FPGA, like hXDP, by adding a compilation step, the Warp Optimizer, and a new hardware module, the Warp Engine. The Warp Optimizer analyzes the eBPF bytecode, at compilation time. While the general purpose nature of the eBPF programming model complicates the identification of functional tasks from the bytecode, its target machine model, with registers assigned with specific functions, allows us to simplify the problem by introducing assumptions such as prior knowledge

8

of the memory areas hosting a packet's data. Therefore, we can identify common packet processing tasks, including packet header parsing and classification, and delegate their execution to the Warp Engine.

#### 1.3 State of the Art

Including programmable accelerators on the Network Interface Card (NIC) is one of the promising approaches to offload the resource-intensive packet processing tasks from the CPU, thereby saving its precious cycles for tasks that cannot be performed elsewhere. Nonetheless, achieving programmability for high-performance network packet processing tasks is an open research problem, with solutions exploring different areas of the solution space that compromise in different ways between performance, flexibility, and ease-of-use [43].

As a result, today's accelerators are implemented using different technologies, including Application-Specific Integrated Circuits (ASICs), Field-Programmable Gate Arrays (FP-GAs), and many-core System-on-Chip. FPGA-based NICs are especially interesting since they provide good performance and a high degree of flexibility, enabling programmers to define virtually any function, provided that it fits in the available hardware resources. Compared to other accelerators for NICs, such as network processing ASICs [14] or many-core System-on-Chip SmartNICs [46], the FPGA NICs flexibility also gives the additional benefit of supporting diverse accelerators for a broader set of applications. For instance, Microsoft employs them in datacenters for network and machine learning tasks [17, 20]. In telecom networks, they are also used to perform radio signal processing tasks [32, 63, 45].

A large number of new NIC designs appeared in the last few years [49, 24, 31, 47, 64, 38]. These solutions mostly combine different compute and network modules in a mix-and-match manner, e.g., regular NIC's switching ASICs with general-purpose compute clusters

based on RISC cores [47], or FPGA-enhanced switching combined with general-purpose clusters [31, 64]. In many solutions, a novelty factor enables P4-based programming of the switching ASIC. This effectively corresponds to replacing the fixed-function switching module with a programmable switching module [49]. Some of these designs offer (partial) eBPF support. However, they implement eBPF on top of the general purpose clusters, replicating the architecture commonly used in server machines, but on a smaller scale. In research, previous work addresses the challenges of moving data among these modules [36], and explores ways to leverage these new NIC designs to improve application performance [66, 21, 17, 35, 37, 50, 52]. Program warping focuses on the design of the packet switching module, targeting FPGA NICs and presenting a solution that integrates with Linux applications that leverage eBPF/XDP. We extend hXDP [56], which is the only solution providing full support for XDP on FPGA NIC directly within the switching module. Compared to hXDP, we provide better performance by introducing a new compilation step co-designed with a hardware module, the Warp Engine, which is pipelined to the hXDP processor.

Recent work addressed eBPF program's optimization at compile time, targeting x86 processors [42, 65]. These works focus on implementing compiler techniques targeting a fixed processor design, whereas we co-design the compiler and the hardware executor. Another related work is Gallium [66], which targets offloading a program's part to programmable switching ASICs. Also, in this case, it assumes a fixed set of executors, including programmable switching chips and processors.

#### 1.4 Structure of the Dissertation

The remainder of this Dissertation is structured as follows.

• Chapter 2, Modern Networks Overview, reviews some of the breakthroughs

of the last decade in computer network organization and design.

- Chapter 3, Sephirot: a Very-Long Instruction Word Processor for Networking Applications, analyzes the details of a fully-pipelined, Very-Long Instruction Word (VLIW) processor executing native eBPF instructions.

- Chapter 4, hXDP: Software Packet Processing on FPGA NICs, introduces a novel datapath that allows the offloading of the eBPF kernel functionalities to an FPGA-based Smart NIC.

- Chapter 5, Program Warping: Faster Hardware Packet Processing, examines a new technique that improves throughput by replacing several instructions of a packet processing program described in eBPF with an equivalent runtime programmable hardware implementation based on TCAMs and programmable parsers.

We conclude the Dissertation with final remarks, summarizing the contributions and results of this work.

#### 1.4.1 List of Published Material

I have (co-)authored the following publications and manuscripts:

- Marco Spaziani Brunella, Giacomo Belocchi, Marco Bonola, Salvatore Pontarelli,

Giuseppe Siracusano, Giuseppe Bianchi, Aniello Cammarano, Alessandro Palumbo,

Luca Petrucci, and Roberto Bifulco. hXDP: Efficient Software Packet Processing

on FPGA NICs f. Commun. ACM, 65(8):92–100, jul 2022

- Marco Spaziani Brunella, Giacomo Belocchi, Marco Bonola, Salvatore Pontarelli, Giuseppe Siracusano, Giuseppe Bianchi, Aniello Cammarano, Alessandro Palumbo, Luca Petrucci, and Roberto Bifulco. hXDP: Efficient Software Packet Processing on FPGA NICs. In 14th USENIX Symposium on Operating Systems Design and Implementation (OSDI 20), pages 973–990. USENIX Association, November 2020

- Marco Bonola, Giacomo Belocchi, Angelo Tulumello, Marco Spaziani Brunella, Giuseppe Siracusano, Giuseppe Bianchi, and Roberto Bifulco. Faster software packet processing on FPGA NICs with eBPF program warping. In 2022 USENIX Annual Technical Conference (USENIX ATC 22), pages 987–1004, Carlsbad, CA, July 2022. USENIX Association

- Salvatore Pontarelli, Roberto Bifulco, Marco Bonola, Carmelo Cascone, Marco Spaziani Brunella, Valerio Bruschi, Davide Sanvito, Giuseppe Siracusano, Antonio Capone, Michio Honda, Felipe Huici, and Giuseppe Siracusano. Flowblaze: Stateful packet processing in hardware. In 16th USENIX Symposium on Networked Systems Design and Implementation (NSDI 19), Boston, MA, 2019. USENIX Association

- Marco Spaziani Brunella, Salvatore Pontarelli, Marco Bonola, and Giuseppe Bianchi. V-PMP: A VLIW packet manipulator processor. In 2018 European Conference on Networks and Communications (EuCNC), pages 1–9. IEEE, 2018

- Marco Spaziani Brunella, Salvatore Pontarelli, Fabrizio Marrese, Marco Bonola, and Giuseppe Bianchi. Packet Manipulator Processor: A RISC-V VLIW core for networking applications. In 7th RISC-V Workshop

- Marco Spaziani Brunella, G. Bianchi, S. Turco, F. Quaglia, and N. Blefari-Melazzi. Foreshadow-vmm: Feasibility and network perspective. In 2019 IEEE Conference on Network Softwarization (NetSoft), pages 257–259, 2019

- Marco Spaziani Brunella, Sara Turco, Giuseppe Bianchi, and Nicola Blefari Melazzi. Foreshadow-VMM: on the practical feasibility of L1 cache Terminal Fault attacks. In 2019 ITASEC

- A. Nannarelli, M. Re, G. C. Cardarilli, L. Di Nunzio, Marco Spaziani Brunella,

R. Fazzolari, and F. Carbonari. Robust throughput boosting for low latency dynamic

12

partial reconfiguration. In 2017 30th IEEE International System-on-Chip Conference (SOCC), 2017

# Chapter 2

### Modern Networks Overview

In this chapter, we are going to review some of the breakthroughs of the last 10 years in computer network design. A consistent part of the chapter will be dedicated to eBPF, which will be the target *Instruction Set Architecture* for V-PMP.

#### 2.1 Software-Defined Networking

An IP network element (NE) appears to external entities as a monolithic piece of network equipment, e.g., a router, NAT, firewall, or load balancer. Internally, however, an IP network element (NE) is composed of numerous logically separated entities that cooperate to provide a given functionality, such as routing. Two types of network element components exist: the control element (CE) in the control plane and the forwarding element (FE) in the data plane. Forwarding elements are typically ASIC, network-processor, or general-purpose processor-based devices that handle data path operations for each packet. Control elements are typically based on general-purpose processors that provide control functionality, like routing and signaling protocols.

In Software Defined Networks [34], most of the control plane software is removed from the route processor card, and instead re-implemented for execution on external commodity hosts, which are under the control of the cloud/Internet service provider. The SDN controller software can hence be maintained and upgraded to support new features by the provider itself, without having to wait for the switch vendor to make modifications. Software Defined Networking is arguably one of the most influential innovations that emerged in the last years in the field of computer networks. The SDN concept is seen as a key enabling technology to provide flexibility and configurability of complex networks. In particular, the use of SDN devices allows easy upgrading of the current protocols and simplifies the adoption of new protocols without requiring to change in the actual hardware devices deployed in the network.

Unfortunately, the programmability of the Software Defined Network cannot be provided by using common hardware architectures such as general purpose CPU but requires the design of specific hardware-based architectures able to forward network traffic with an aggregated bandwidth up to multiple terabits/sec.

The most adopted SDN architecture is based on [41], a pragmatic and viable platform agnostic interface to the network switch hardware. In particular, this abstraction provides a match, action mechanism to modify a packet traversing the network switch pipeline. The use of multiple match stages in the pipeline permits great increases in the packet throughput since the device is able to perform several queries in parallel.

Considering that in each query the packet header must be checked against thousands of rules stored in the match tables, it is evident that a CPU-based architecture cannot sustain the same throughput that can be provided by specific hardware for pattern matching such as Ternary Content Addressable Memories (TCAMs), binary Content Addressable Memories (CAMs) [48] or exact matching engines based on multiple hash tables [53].

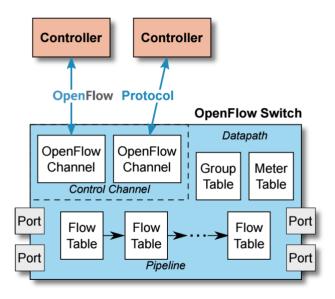

#### 2.1.1 The OpenFlow Protocol

OpenFlow provides an open protocol to program the flow table in different switches and routers.

The datapath of an OpenFlow Switch consists of a Flow Table and an action associated with each flow entry, as depicted in Fig.2.1.

For high performance and low cost, the data path must have a carefully prescribed degree of flexibility. This means forgoing the ability to specify arbitrary handling of each packet and seeking a more limited, but still useful, range of actions.

An OpenFlow Switch consists of at least three parts:

- A Flow Table, with an action associated with each flow entry, to tell the switch how to process the flow

- A Secure Channel that connects the switch to the controller, allowing commands and packets to be sent between a controller and the switch

- The OpenFlow Protocol, which provides an open and standard way for a controller to communicate with a switch.

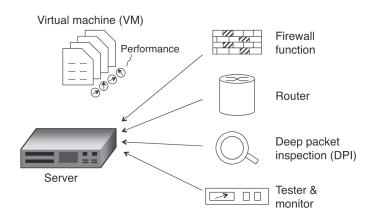

#### 2.2 Network Function Virtualization

Network Function Virtualization (NFV) [7] is a term used to represent the implementation of data plane network functions in software that is executed on commodity hosts, as depicted in Fig.2.2 .

The hypothesis is that NFV will incur lower capital expenditures and operating expenditures when compared to traditional switches/routers and middlebox appliances in which data plane network functions are typically implemented in custom hardware.

The architectural components of NFV are:

Figure 2.1: Typical OpenFlow architecture

- Network Function Virtualization Infrastructure (NFVI)

- Network Functions (NFs),

- Management And Network Orchestration (MANO)

The infrastructure consists of hardware (a single computer or a compute cluster), and framework software, which offers functions that are commonly required by NFs, such as NF placement, dynamic scaling, etc.

Data-plane network functions considered for software implementation in commodity hosts range from basic packet forwarding to complex middlebox functions such as intrusion prevention systems. When NFs are executed on Virtual Machines (VMs), they are referred to as Virtual Network Functions (VNFs). MANO components include management functions, such as Fault management, Configuration management, Accounting, Performance monitoring, and Security, and orchestrators, which manage service chains of multiple NFs.

Figure 2.2: Network Function Virtualization concept

#### 2.3 Berkeley Packet Filter

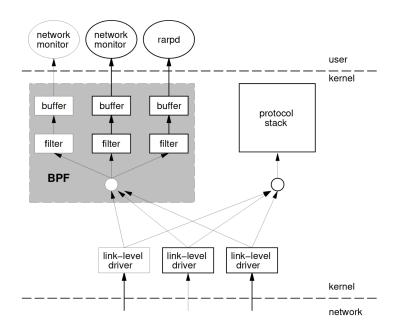

Berkeley Packet Filter (BPF) [40] is an in-kernel virtual machine for packet filtering. BPF has two main components: the network tap and the packet filter. The network tap collects copies of packets from the network device drivers and delivers them to listening applications, as depicted in Fig.2.3.

The filter decides if a packet should be accepted and, if so, how much of it to copy to the listening application. When a packet arrives at a network interface, the link-level device driver normally sends it up the system protocol stack. But when BPF is listening on this interface, the driver first calls BPF. BPF feeds the packet to each participating processfilter.

This user-defined filter decides whether a packet is to be accepted and how many bytes of each packet should be saved. For each filter that accepts the packet, BPF copies the requested amount of data to the buffer associated with that filter. The device driver then regains control. If the packet was not addressed to the local host, the driver returns from the interrupt. Otherwise, normal protocol processing proceeds.

Figure 2.3: BPF architecture

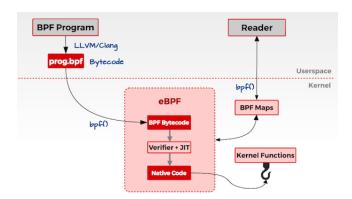

BPF has been extended to exploit the full power of the 64-bit architectures of modern processors, thus leading to extended BPF. Whilst providing the same functionalities of classic BPF, there are several appealing new features in eBPF: it can execute arbitrary code, permit fast dynamic recompilation, and provides an efficient interface with the userland. The main characteristic of eBPF is to provide dynamic programmability at the kernel level without compromising the operating system's security and stability. This is possible since the eBPF programs must fulfill a set of tight requirements: eBPF program always terminates, does not contain loops and pointer arithmetic is prohibited. Furthermore, the use of helper functions (special functions restricted to a white list defined in the kernel) greatly extends the capability of eBPF to perform network processing tasks and to interact with the system.

The main components of the eBPF framework are:

#### • eBPF Virtual Machine

- Maps

- Helper Functions

The architecture of eBPF is illustrated in Fig.2.4.

Figure 2.4: eBPF architecture

#### 2.3.1 eBPF Virtual Machine

eBPF is a RISC register machine with a total of 11 64-bit registers, a program counter, and a 512-byte fixed-size stack. 9 registers are general-purpose read-write, one is a read-only stack pointer and the program counter is implicit, i.e. we can only jump to a certain offset from it. The VM registers are always 64-bit wide and support 32-bit subregister addressing if the most significant bits of the registers are zeroed.

Each function call can have at most 5 arguments in registers r1-r5; this applies to both ebpf-to-ebpf calls and to kernel function calls. Registers r1-r5 can only store numbers or pointers to the stack (to be passed as arguments to functions), never direct pointers to arbitrary memory. All memory accesses must be done by first loading data to the eBPF stack before using it in the eBPF program. This restriction helps the eBPF verifier, it simplifies the memory model to enable easier correctness checking.

20

#### 2.3.2 eBPF Instruction Set Architecture

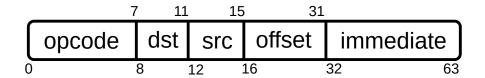

eBPF encodes its instructions in a similar way to what a standard MIPS architecture would do. They are fixed length, 64bit wide instructions, as depicted in **Fig. 2.5**.

Figure 2.5: eBPF Instruction Encoding

Instructions are divide with respect to the functional unit they use:

- ALU64

- ALU32

- Memory

- $\bullet$  Branch

The complete ISA is reported in the following tables.

| Opcode | Mnemonic      | Pseudocode              |

|--------|---------------|-------------------------|

| 0x07   | add dst, imm  | dst + = imm             |

| 0x0f   | add dst, src  | dst + = src             |

| 0x17   | sub dst, imm  | dst -= imm              |

| 0x1f   | sub dst, src  | dst -= src              |

| 0x27   | mul dst, imm  | dst *= imm              |

| 0x2f   | mul dst, src  | dst *= src              |

| 0x37   | div dst, imm  | dst / = imm             |

| 0x3f   | div dst, src  | dst / = src             |

| 0x47   | or dst, imm   | $dst \mid = imm$        |

| 0x4f   | or dst, src   | $dst \mid = src$        |

| 0x57   | and dst, imm  | dst & = imm             |

| 0x5f   | and dst, src  | dst & = src             |

| 0x67   | lsh dst, imm  | dst <<= imm             |

| 0x6f   | lsh dst, src  | dst <<= src             |

| 0x77   | rsh dst, imm  | dst >>= imm(logical)    |

| 0x7f   | rsh dst, src  | dst >>= src(logical)    |

| 0x87   | neg dst       | dst = -dst              |

| 0x97   | mod dst, imm  | dst % = imm             |

| 0x9f   | mod dst, src  | dst % = src             |

| 0xa7   | xor dst, imm  | $dst \oplus = imm$      |

| 0xaf   | xor dst, src  | $dst \oplus = src$      |

| 0xb7   | mov dst, imm  | dst = imm               |

| 0xbf   | mov dst, src  | dst = src               |

| 0xc7   | arsh dst, imm | dst >>= imm(arithmetic) |

| 0xcf   | arsh dst, srs | dst >>= src(arithmetic) |

Table 2.1: ALU 64 Instructions

| Opcode | Mnemonic        | Pseudocode              |

|--------|-----------------|-------------------------|

| 0x04   | add32 dst, imm  | dst + = imm             |

| 0x0c   | add32 dst, src  | dst + = src             |

| 0x14   | sub32 dst, imm  | dst -= imm              |

| 0x1c   | sub32 dst, src  | dst -= src              |

| 0x24   | mul32 dst, imm  | dst *= imm              |

| 0x2c   | mul32 dst, src  | dst *= src              |

| 0x34   | div32 dst, imm  | dst / = imm             |

| 0x3c   | div32 dst, src  | dst / = src             |

| 0x44   | or32 dst, imm   | $dst \mid = imm$        |

| 0x4c   | or32 dst, src   | $dst \mid = src$        |

| 0x54   | and32 dst, imm  | dst & = imm             |

| 0x5c   | and32 dst, src  | dst & = src             |

| 0x64   | lsh32 dst, imm  | dst <<= imm             |

| 0x6c   | lsh32 dst, src  | dst <<= src             |

| 0x74   | rsh32 dst, imm  | dst >>= imm(logical)    |

| 0x7c   | rsh32 dst, src  | dst >>= src(logical)    |

| 0x84   | neg32 dst       | dst = -dst              |

| 0x94   | mod32 dst, imm  | dst % = imm             |

| 0x9c   | mod32 dst, src  | dst % = src             |

| 0xa4   | xor32 dst, imm  | $dst \oplus = imm$      |

| 0xac   | xor32 dst, src  | $dst \oplus = src$      |

| 0xb4   | mov32 dst, imm  | dst = imm               |

| 0xbc   | mov32 dst, src  | dst = src               |

| 0xc4   | arsh32 dst, imm | dst>>= imm(arithmetic)  |

| 0xcc   | arsh32 dst, srs | dst >>= src(arithmetic) |

Table 2.2: ALU 32 Instructions

| Opcode            | Mnemonic | Pseudocode         |

|-------------------|----------|--------------------|

| 0xd4  (imm == 16) | le16 dst | dst = htole16(dst) |

| 0xd4  (imm == 32) | le32 dst | dst = htole32(dst) |

| 0xd4  (imm == 64) | le64 dst | dst = htole64(dst) |

| 0xdc (imm == 16)  | be16 dst | dst = htobe16(dst) |

| 0xdc (imm == 32)  | be32 dst | dst = htobe32(dst) |

| 0xdc (imm == 64)  | be64 dst | dst = htobe64(dst) |

Table 2.3: Byteswap Instructions

| Opcode | Mnemonic             | Pseudocode                       |

|--------|----------------------|----------------------------------|

| 0x18   | lddw dst             | dst = imm                        |

| 0x20   | ldabsw src           | See kernel documentation         |

| 0x28   | ldabsh src           |                                  |

| 0x30   | ldabsb src           |                                  |

| 0x38   | ldabsdw src          |                                  |

| 0x40   | ldindw src           |                                  |

| 0x48   | ldindh src           |                                  |

| 0x50   | ldindb src           |                                  |

| 0x58   | ldinddw src          |                                  |

| 0x61   | ldxw dst, [src+off]  | $dst = *(uint32\_t*)(src + off)$ |

| 0x69   | ldxh dst, [src+off]  | $dst = *(uint16\_t*)(src + off)$ |

| 0x71   | ldxb dst, [src+off]  | $dst = *(uint8\_t*)(src + off)$  |

| 0x79   | ldxdw dst, [src+off] | $dst = *(uint64\_t*)(src + off)$ |

| 0x62   | stw [dst+off], imm   | $*(uint32\_t*)(dst + off) = imm$ |

| 0x6a   | sth [dst+off], imm   | $*(uint16_t*)(dst + off) = imm$  |

| 0x72   | stb [dst+off], imm   | $*(uint8\_t*)(dst + off) = imm$  |

| 0x7a   | stdw [dst+off], imm  | $*(uint64_t*)(dst + off) = imm$  |

| 0x63   | stxw [dst+off], src  | $*(uint32\_t*)(dst + off) = src$ |

| 0x6b   | stxh [dst+off], src  | $*(uint16\_t*)(dst + off) = src$ |

| 0x73   | stxb [dst+off], src  | $*(uint8\_t*)(dst + off) = src$  |

| 0x7b   | stxdw [dst+off], src | $*(uint64_t*)(dst + off) = src$  |

Table 2.4: Memory Instructions

| Opcode | Mnemonic            | Pseudocode                             |

|--------|---------------------|----------------------------------------|

| 0x05   | ja +off             | PC+=off                                |

| 0x15   | jeq dst, imm, +off  | $PC + = off \ if \ dst == imm$         |

| 0x1d   | jeq dst, src, +off  | $PC + = off \ if \ dst == src$         |

| 0x25   | jgt dst, imm, +off  | $PC+=off\ if\ dst>imm$                 |

| 0x2d   | jgt dst, src, +off  | $PC+=off\ if\ dst>src$                 |

| 0x35   | jge dst, imm, +off  | $PC+=off\ if\ dst>=imm$                |

| 0x3d   | jge dst, src, +off  | $PC+ = off \ if \ dst > = src$         |

| 0xa5   | jlt dst, imm, +off  | $PC + = off \ if \ dst < imm$          |

| 0xad   | jlt dst, src, +off  | $PC + = off \ if \ dst < src$          |

| 0xb5   | jle dst, imm, +off  | $PC + = off \ if \ dst < = imm$        |

| 0xbd   | jle dst, src, +off  | $PC + = off \ if \ dst <= src$         |

| 0x45   | jset dst, imm, +off | $PC + = off \ if \ dst\&imm$           |

| 0x4d   | jset dst, src, +off | $PC + = off \ if \ dst\&src$           |

| 0x55   | jne dst, imm, +off  | $PC + = off \ if \ dst! = imm$         |

| 0x5d   | jne dst, src, +off  | $PC + = off \ if \ dst! = src$         |

| 0x65   | jsgt dst, imm, +off | $PC+=off\ if\ dst>imm(signed)$         |

| 0x6d   | jsgt dst, src, +off | $PC+=off\ if\ dst>src(signed)$         |

| 0x75   | jsge dst, imm, +off | $PC+=off\ if\ dst>=imm(signed)$        |

| 0x7d   | jsge dst, src, +off | $PC+=off\ if\ dst>=src(signed)$        |

| 0xc5   | jslt dst, imm, +off | $PC + = off \ if \ dst < imm(signed)$  |

| 0xcd   | jslt dst, src, +off | $PC + = off \ if \ dst < src(signed)$  |

| 0xd5   | jsle dst, imm, +off | $PC + = off \ if \ dst <= imm(signed)$ |

| 0xdd   | jsle dst, src, +off | $PC+=off\ if\ dst <= src(signed)$      |

| 0x85   | call imm            | Function call                          |

| 0x95   | exit                | $return \ r0$                          |

Table 2.5: Branch Instructions

#### 2.3.3 Maps

The eBPF maps are a generic data structure for the storage of different data types. When the map is created the user specifies the key type (and thus the size of the key), the value type, and the number of entries supported by the map. eBPF maps are used to keep the state between invocations of the eBPF program, and allow sharing of data between eBPF kernel programs, and also between kernel and user-space applications. eBPF defines several types of maps (12 maps are listed in the Linux implementation of eBPF<sup>1</sup>).

The main ones are:

- BPF\_MAP\_TYPE\_HASH: this map provides an hash table where the  $\langle key, value \rangle$  pairs are stored.

- BPF\_MAP\_TYPE\_ARRAY: this is an array of memory locations.

- BPF\_MAP\_TYPE\_PROG\_ARRAY: This is one of the more interesting eBPF-map types because it allows tail calling of eBPF programs.

#### 2.3.4 Helper Functions

The eBPF helper is a special function that can be called from within eBPF programs to perform a variety of tasks. The helper function can be used by eBPF programs to interact with the system. This is useful for debugging the kernel and carrying out performance analysis. Helper functions can be also used to interact with eBPF maps or to handle network packets. The helper functions are restricted to a defined white list to guarantee kernel security and stability. Calling helpers functions in the Linux implementation introduces no overhead, because of the direct call into the compiled helper, and so excellent performance is offered.

<sup>&</sup>lt;sup>1</sup>a complete list of the eBPF maps is available here: https://ferrisellis.com/posts/ebpf\\_syscall\_and\_maps/

#### 2.4 eXpress Data Path

XDP allows programmers to inject programs at the NIC driver level so that such programs are executed before a network packet is passed to the Linux's network stack. XDP programs are based on Linux's eBPF technology. eBPF provides an in-kernel virtual machine for the sandboxed execution of small programs within the kernel context. In its current version, the eBPF virtual machine has 11 64b registers: r0 holds the return value from in-kernel functions and programs, r1 - r5 are used to store arguments that are passed to in-kernel functions, r6 - r9 are registers that are preserved during function calls and r10 stores the frame pointer to access the stack. The eBPF virtual machine has a well-defined ISA composed of more than 100 fixed-length instructions (64b). Programmers usually write an eBPF program using the C language with some restrictions, which simplifies the static verification of the program.

eBPF programs can also access kernel memory areas called maps, i.e., kernel memory locations that essentially resemble tables. For instance, eBPF programs can use maps to implement arrays and hash tables. An eBPF program can interact with the map's locations by means of pointer deference, for unstructured data access, or by invoking specific helper functions for structured data access, e.g., a lookup on a map configured as a hash table. Maps are especially important since they are the only means to keep state across program executions and to share information with other eBPF programs and with programs running in user space.

# Chapter 3

# Sephirot: a Very-Long Instruction Word Processor for Networking Applications

In this chapter, we analyze the details of Sephirot: a fully-pipelined, Very-Long Instruction Word (VLIW) processor executing native eBPF instructions. A VLIW processor can execute multiple concurrent micro-instructions on its different execution *lanes*. In contrast to what happens in a super-scalar CPU, where two (or more) instructions are determined to be run concurrently at run-time, that is, inside the hardware, in a VLIW processor, the complexity of instruction's group formation is moved to the compiler, which *packs* multiple micro-instructions into, ipso facto, Very-Long Instruction Words.

To understand the principles behind a VLIW processor, let's suppose that these two micro-instructions need to be executed:

```

add $2, $3 ; add to register 2 the content of register 3

mov $1, $3 ; move the content of register 3 to register 1

```

To execute the mov instruction, no information about the result of the add is needed. Thus the two instructions can be executed concurrently, thus exploiting the Instruction Level Parallelism intrinsic of this stream of instructions.

To formalize this process, we can use Bernstein's conditions [9].

#### Bernstein's conditions

Suppose we have two instructions,  $P_1$ , and  $P_2$ . To tell whether the two instructions are independent - thus can be parallelized - they need to match 3 requirements:

$$I_1 \cap O_2 = \emptyset$$

$$I_2 \cap O_1 = \emptyset$$

$$O_2 \cap O_1 = \emptyset$$

Where  $I_i$  is the set of inputs required for the  $i^{th}$  instruction to execute, while the  $O_i$  is the set of output resources of the  $i^{th}$  instruction.

The first two conditions impose that the inputs of one of the two instructions do not depend on the outputs of the other one, while the last condition imposes that the two instruction do not write to the same resource - e.g., the same register -.

For more than two instructions, the number of conditions to be checked for dependencies grows with the square of the number of instructions.

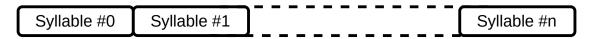

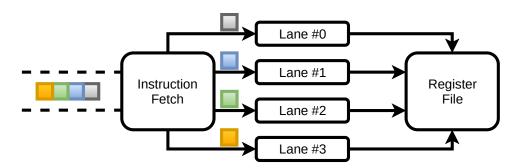

Once two instructions, called *syllables*, can be grouped for concurrent execution, they are *packed* to form a very-long instruction, as depicted in **Fig. 3.1**. The very-long instruction word is then executed by the CPU, which takes the VLIW, chops that into *syllables*,

and then sends each syllable to an execution lane, as depicted in **Fig. 3.2**. Each lane implements an independent pipeline.

Figure 3.1: VLIW Instruction

Figure 3.2: Very-Long Instruction Word architecture

The task of packing the instructions into parallelized syllables is entirely offloaded to the compiler in a VLIW architecture, allowing the hardware to be fast and efficient. When a package of syllables cannot be completed because the compiler wasn't able to find any other parallelizable instruction, it fills the syllable with a **nop** syllable, which instructs the relevant lane not to do anything.

Thus, the theoretical speedup is n times, where n is the number of lanes available in the architecture. More realistically, we estimate the speedup to be roughly  $\frac{n}{2}$  since not always the compiler can parallelize syllables.

From the hardware side, the real problem is posed by the register file, which needs to implement an n port RAM. For this reason, the number of parallel lanes and registers is typically inversely proportional.

In the rest of the chapter, we detail the design choices made for a particular use case. Sephirot has been integrated as an execution unit inside a programmable network datapath called hXDP, which aims at offloading the eBPF functionalities from the Kernel to the FPGA. With this in mind, Sephirot has been crafted to map exactly the resources of the eBPF virtual machine.

We perform a Design-Space exploration of different numbers and kinds of parallel lanes, resulting in a critical analysis of the network workloads involved.

#### 3.1 Sephirot architecture

As previously introduced, a VLIW CPU architecture can execute multiple instructions in parallel by using n syllables, each long m bits, concatenated to form a unique very-long word. All syllables are executed in parallel by a dedicated lane of the CPU, which is composed of a fetch stage (IF), a decode stage (SD), and an execute stage (SE).

In the particular case of Sephirot, the width of the instruction is 256 bits, allowing the simultaneous execution of four 64-bit syllables on four different lanes. The syllables represent a single eBPF instruction.

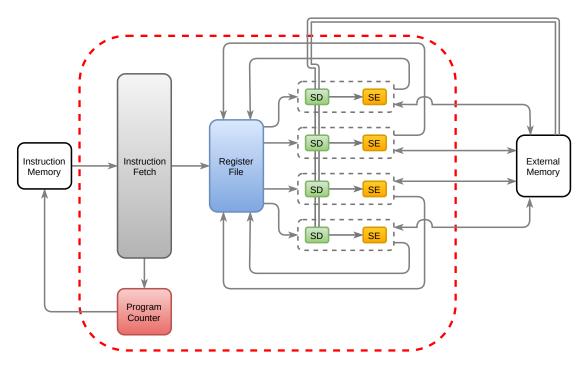

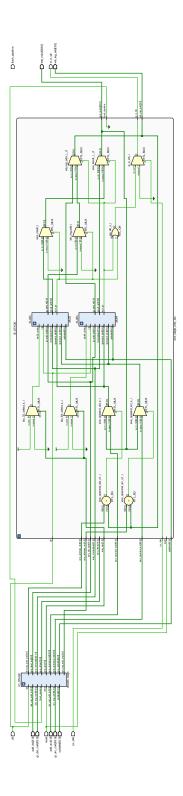

The top-view architecture of Sephirot is depicted in Figure 3.3.

Taking as reference a standard CPU, such as the MIPS CPU used in [51], this architecture can provide a theoretical 4x instruction throughput<sup>1</sup>.

The Sephirot architecture differs from a standard VLIW processor for several design choices that we identified as mandatory to obtain high throughput in the specific task of packet manipulation, such as:

<sup>&</sup>lt;sup>1</sup>The actual improvement can be less than 4x since the four syllables can be executed in parallel only if they are mutually independent. Suppose there are fewer than four independent syllables to execute. In that case, the VLIW instruction is filled by NOP operations, and the actual improvement of the VLIW architecture to a standard architecture decreases.

Figure 3.3: Sephirot architecture

- Memory & registers prefetch

- Multiple memory units

- Short pipeline

The need for memory and internal registers prefetch arises from the high memory pressure required in header rewriting and data movement. Since requesting data from memory and registers takes an additional clock cycle, data is queried to these units in advance to have the requested data ready when needed in the syllable execution phase. In particular, for the operations involving operands stored in the register file, operands are queried already in the fetch stage, directly latched in the pipeline register of the decode stage, and finally provided to the execute stage without stalls. Similarly, the data is queried from memory already in the decode stage for load operations from memory. For the same reason, PMP allows four memory units to execute operations on the memory in

parallel, allowing 256 bits per clock cycle to be moved from/to memory.

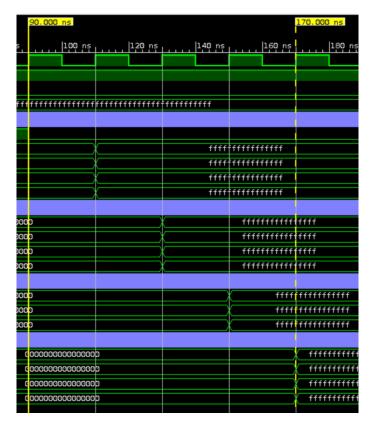

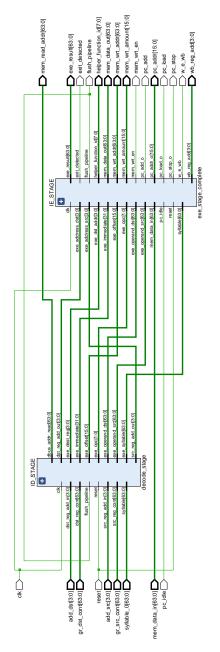

The core has been thoroughly simulated using Vivado 2017.4, and a snapshot of the simulation is depicted in **Fig. 3.4**, in which the pipeline timing is highlighted.

Figure 3.4: Sephirot Pipeline Simulation

As in almost all the pipelined CPU architectures, the management of branches can significantly affect the performance of Sephirot. If a branch is taken, the instructions that are in the fetch and decode stages could be invalid, resulting in what is usually called misprediction. When a branch instruction is processed, the next instruction to be executed is known only at the end of the execute stage.

Although stalling the pipeline and waiting for the result of the branch instruction is a possible solution, it decreases the microprocessor performance. Instead, we implemented

a simple speculative execution mechanism that always assumes that the branch is not taken, starting executing instruction right after the fetch of the branch instruction. The misprediction costs several clock cycles equal to the depth of the pipeline. For this reason, Sephirot implements a very short pipeline, having the branch misprediction penalty quantifiable in 4 clock cycles. Every stage takes exactly one clock cycle to be executed. Using pipelining registers between the fetch, decode, and execute stages allows the execution of a complete instruction (4 syllables) per clock cycle.

Another issue arising from the use of a pipelined architecture is the fact that consecutive dependent instructions will encounter a data hazard. If an instruction in the decode stage depends on the results of another instruction that is in the execute stage, it will get the old value of the data stored in the registers. The new one will only be written on the register file on the next clock cycle.

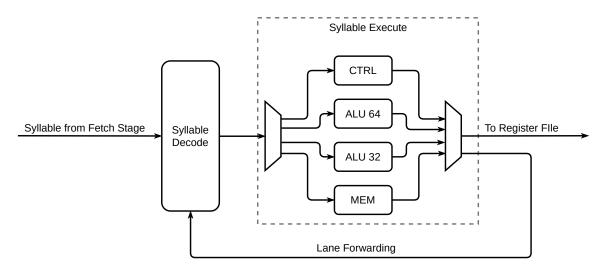

To overcome this issue, *lane forwarding* has been implemented. In this way, when a syllable is in the execute stage, it sends its result not only to the register file but also to the decode stage. This allows the instruction in the decode stage to always have the updated value. The details of each lane are depicted in **Fig. 3.5**.

Figure 3.5: Sephirot Lane Architecture

The first optimization in area occupancy has been achieved by noticing that branch instruction cannot be parallelized. Thus, the *control* unit is present only on the first lane. The compiler for the VLIW architecture must take care of placing the branch instructions only on the first lane.

The *Program Counter* unit provides the address for the next instruction to be fetched from the instruction memory. It also implements a finite-state machine to handle control signals at each pipeline stage. In particular, when a branch is taken, the program counter unit flushes the pipeline. This unit is also responsible for stalling the pipeline and calling the correct eBPF helper function when a call syllable is executed.

The Register File is a 4-port RAM with 11 64-bit wide locations. That map precisely the ones of the eBPF virtual machine.

## 3.2 Synthesis Results

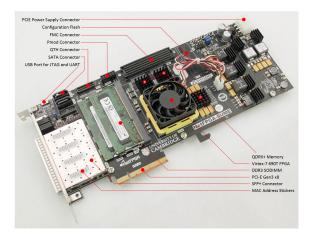

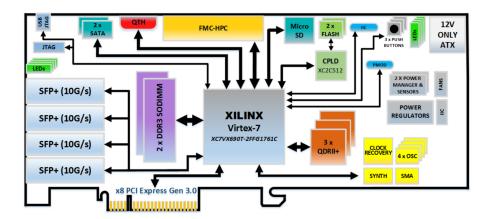

The core has been synthesized on a NetFPGA Sume [67], a Virtex-7-based board specifically designed for networking applications. The board is depicted in **Fig. 3.6**.

Figure 3.6: NetFPGA SUME

The NetFPGA SUME design aims to create a low-cost, PCIe host adapter card able to support 40Gb/s and 100Gb/s applications. The NetFPGA SUME uses a large FPGA, supporting high-speed serial interfaces of 10Gb/s or more presented both in standard interfaces (SFP+) and in a format that permits easy user-expansion, a large and extensible quantity of high-speed DRAM, alongside a quantity of high-throughput SRAM, and all this constrained by a desire for low cost to enable access by the wider research and academic communities. The block diagram of the NetFPFA SUME is reported in **Fig. 3.7**.

Figure 3.7: NetFPGA SUME block Diagram

#### 3.2.1 Full-core Synthesis

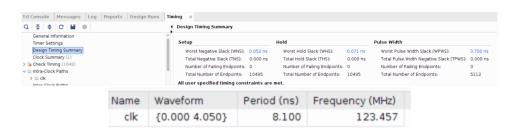

The results of the synthesis of the core are given in **Table 3.1**. To achieve timing closure, retiming has been enabled in Vivados's synthesizer. This allowed the synthesizer to add pipelining registers to cut the critical path without altering the timing of the CPU.

Unsurprisingly, the critical path was due to the large adder inside the 64-bit ALU. In fact, the Virtex-7 provides specialized blocks called *DSP48* [62] to allow fast arithmetic operations in the FPGA fabric, without generating distributed adders.

| Resource Type | Used  | Available | Utilization % |

|---------------|-------|-----------|---------------|

| Slice LUTs    | 19559 | 433200    | 4.52%         |

| Slice FFs     | 5111  | 866400    | 0.59%         |

| F7 Muxes      | 1030  | 216600    | 0.48%         |

| F8 Muxes      | 512   | 108300    | 0.47%         |

| DSP48E1       | 40    | 3600      | 1.11%         |

Table 3.1: Sephirot full core utilization

The problem is that the input size of those adders is limited to 48 bits, while our operands are of 64bits, thus having the remaining 16 bits implemented as a distributed adder. Despite this, a frequency of  $123 \ MHz$  has been achieved in all the variants of Sephirot.

The results of the timing are given inf Fig. 3.8.

Figure 3.8: Full-core timing report

On the overall occupancy, the impact of the register file is detailed in **Table 3.2**, while the occupancy of a single lane is detailed in **Table 3.3**.

| Resource Type | Used | Available | Utilization % |

|---------------|------|-----------|---------------|

| Slice LUTs    | 3977 | 433200    | 0.92%         |

| Slice FFs     | 2016 | 866400    | 0.23%         |

| F7 Muxes      | 1024 | 216600    | 0.47%         |

| F8 Muxes      | 512  | 108300    | 0.47%         |

Table 3.2: 4-Port register file utilization

| Resource Type | Used | Available | Utilization % |

|---------------|------|-----------|---------------|

| Slice LUTs    | 4394 | 433200    | 1.01%         |

| Slice FFs     | 683  | 866400    | 0.08%         |

| F7 Muxes      | 2    | 216600    | < 0.01%       |

| F8 Muxes      | 0    | 108300    | 0%            |

| DSP48E1       | 10   | 3600      | 0.28%         |

Table 3.3: Full lane utilization

From the reports, we can derive that the hardware footprint of Sephirot is indeed very low and that, even if the register file cannot be synthesized as a *Block RAM*, the impact of a distributed approach on area and performance is not remarkable.

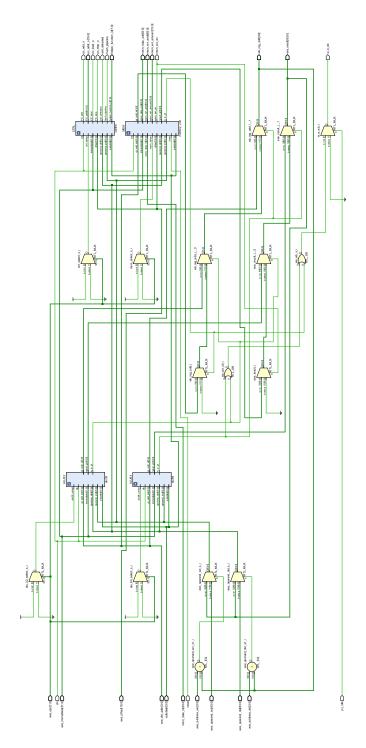

The synthesized lane is depicted in **Fig. 3.9**, while the complete execution unit is depicted in **Fig. 3.10**.

Figure 3.9: Synthesized Lane Schematic

Figure 3.10: Synthesized Execution Unit Schematic

#### 3.3 Performance-Area Tradeoff

In this section, we provide an analysis of the achievable Instruction Level Parallelism that can be reached on some of the examples of eBPF contained in the Linux kernel documentation.

This kind of analysis will drive us to the final architecture of Sephirot. In fact, the previous architecture was just a baseline, with a homogeneous structure of the 4 lanes.

For comparison, also a 2-lane architecture has been considered and implemented successfully.

#### 3.3.1 ILP Analysis

In order to evaluate how much Instruction Level Parallelism is achievable, we need to apply Bernstein's condition. In the specific case of our architecture, one of the 3 conditions can be relaxed.

In fact, the  $I_1 \cap O_2 = \emptyset$  condition does not need to be fulfilled since, even if the output of the second instruction it's equal to the input of the first, there is a one clock cycle delay between the two, thus they can be parallelized. This is the case of *load after store* sequences of instruction. One of the XDP examples on which the analysis has been carried out is reported in the following listing.

```

r6 = r1;

r7 = 1;

r1 = *(u32 *)(r6 + 4);

r2 = *(u32 *)(r6 + 0);

r3 = *(u8 *)(r2 + 12);

= *(u8 *)(r2 + 13);

r4 <<= 8;

10

r4 |= r3;

11

12

r7 = 2;

if r4 != 8 goto +102 < LBB0_9 >;

14

r1 -= r2;

15

r1 <<= 32;

```

```

r1 s>>= 32;

17

r2 = 601;

if r2 s> r1 goto +97 <LBB0-9>;

18

19

r2 = 98;

20

r2 -= r1;

21

\mathrm{r}\,\mathbf{1}\ =\ \mathrm{r}\,\mathbf{6}\ ;

22

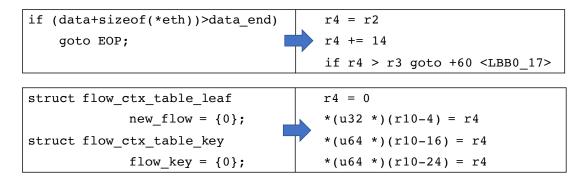

call 65;

23

{\rm r}\,0 \ <<= \ 32 \ ;

24

{\tt r}\, 0 \ >>= \ 3\, 2 \ ;

i\,f\  \  \, r0\  \, !=\  \, 0\  \, \, {\rm goto}\  \, +90\  \, <\! {\rm LBB0\_9}\!>;\\

25

26

r1 = r6;

27

r2 = 4294967268 11;

28

call 44;

29

r0 <<= 32;

30

r0 >>= 32;

31

r7 = 1;

i\,f\  \  \, {\rm r}\,0\  \, !=\  \, 0\  \  \, {\rm goto}\  \  \, +82\  \, {\rm <LBB0\_9>};\\

32

33

r1 = *(u32 *)(r6 + 4);

r6 = *(u32 *)(r6 + 0);

35

r2 = r6;

r2 += 126;

36

37

r7 = 1;

if \quad r2 \ > \ r1 \quad goto \ +76 \ < LBB0\_9>;

39

r1 = *(u8 *)(r6 + 33);

40

*(u8 *)(r6 + 11) = r1;

r1 = *(u8 *)(r6 + 32);

41

42

*(u8 *)(r6 + 10) = r1;

r1 = *(u8 *)(r6 + 31);

43

*(u8 *)(r6 + 9) = r1;

44

45

r1 = *(u8 *)(r6 + 30);

46

*(u8 *)(r6 + 8) = r1;

47

r1 = *(u8 *)(r6 + 29);

48

*(u8 *)(r6 + 7) = r1;

49

r1 = *(u8 *)(r6 + 28);

50

*(u8 *)(r6 + 6) = r1;

r1 = *(u8 *)(r6 + 37);

51

52

*(u8 *)(r6 + 3) = r1;

53

r1 = *(u8 *)(r6 + 36);

*(u8 *)(r6 + 2) = r1;

54

55

r1 = *(u8 *)(r6 + 35);

56

*(u8 *)(r6 + 1) = r1;

57

r1 = *(u8 *)(r6 + 34);

58

*(u8 *)(r6 + 0) = r1;

59

r1 = *(u8 *)(r6 + 39);

60

*(u8 *)(r6 + 5) = r1;

61

r1 = *(u8 *)(r6 + 38);

*(u8 *)(r6 + 4) = r1;

62

r1 = *(u8 *)(r6 + 41);

64

*(u8 *)(r6 + 13) = r1;

r1 = *(u8 *)(r6 + 40);

65

66

*(u8 *)(r6 + 12) = r1;

r1 = 1027;

68

*(u32 *)(r6 + 34) = r1;

69

r1 = 18946;

70

*(u16 *)(r6 + 40) = r1;

71

r3 = r6;

```

```

r3 += 34;

73

r7 = 0;

r1 = 0;

74

75

r2 = 0;

76

r4 = 92;

77

{\bf r}\, {\bf 5} \ = \ 0 \ ;

78

call 28;

79

r1 \; = \; 1879048261 \, ;

80

*(u32 *)(r6 + 14) = r1;

81

r1 = 320;

*(u32 *)(r6 + 22) = r1;

82

83

r1 = *(u32 *)(r6 + 54);

84

*(u32 *)(r6 + 30) = r1;

85

r1 = *(u32 *)(r6 + 58);

*(u32 *)(r6 + 26) = r1;

86

87

r1 = r0;

r1 >>= 16;

88

r1 += r0;

89

r1 \hat{ } = -1;

*(u16 *)(r6 + 36) = r1;

91

92

\mathbf{r3}\ =\ \mathbf{r6}\ ;

93

r3 += 14;

94

r1 = 0;

r2 = 0;

95

r4 = 20;

96

97

r5 = 0;

98

call 28;

99

r1 = r0;

r1 >>= 16;

100

101

r1 += r0;

r\, 1 \ \hat{\ } = \ -1\,;

102

*(u16 *)(r6 + 24) = r1;

103

*(u64 *)(r10 - 8) = r7;

104

105

r2 = r10;

106

r2 += -8;

107

r1 = 0;

108

call 1;

if \quad \texttt{r0} \ == \ 0 \quad \texttt{goto} \ +3 \ \texttt{<LBB0\_8>};

109

r1 = *(u64 *)(r0 + 0);

110

r1 += 1;

111

112

*(u64 *)(r0 + 0) = r1;

113

114

115

LBB0_8:

116

r7 = 3;

117

118

119

{\tt LBB0\_9}:

120

r0 = r7;

121

exit;

```

The same code, executed with 2-lanes can be compressed into the following code:

```

1 | r6 = r1; r7 = 1;

2 | r1 = *(u32 *)(r6 + 4); r2 = *(u32 *)(r6 + 0);

3 r3 = r2;

4 r3 += 14;

5 | if r3 > r1 goto +108 < LBB0_9>;

6 r3 = *(u8 *)(r2 + 12); r4 = *(u8 *)(r2 + 13);

7 r4 <<= 8;

8 | r4 | = r3; r7 = 2;

9 if r4 != 8 goto +102 <LBB0_9>;

10

r1 -= r2;

11 r1 <<= 32;

12 r1 s>>= 32; r2 = 601;

13 if r2 s> r1 goto +97 <LBB0_9>;

14 | r2 = 98;

15 r2 -= r1; r1 = r6;

16 call 65;

17 r0 <<= 32;

18 r0 >>= 32;

19 if r0 != 0 goto +90 <LBB0-9>;

20 | \mathbf{r}1 = \mathbf{r}6; \ \mathbf{r}2 = 4294967268 \ 11;

21 call 44;

22 r0 <<= 32;

23 r0 \gg 32; r7 = 1;

24 if r0 != 0 goto +82 <LBB0_9>;

25 r1 = *(u32 *)(r6 + 4); r6 = *(u32 *)(r6 + 0);

26 r2 = r6;

27 | r2 += 126; r7 = 1;

28 if r2 > r1 goto +76 <LBB0_9>;

29 r1 = *(u8 *)(r6 + 33);

30 \times (u8 \times (r6 + 11) = r1; r1 = *(u8 \times (r6 + 32);

31 \times (u8 \times (r6 + 10) = r1; r1 = *(u8 \times (r6 + 31);

32

*(u8 *)(r6 + 9) = r1; r1 = *(u8 *)(r6 + 30);

33 *(u8 *)(r6 + 8) = r1; r1 = *(u8 *)(r6 + 29);

34 \times (u8 \times) (r6 + 7) = r1; r1 = *(u8 \times) (r6 + 28);

35 \times (u8 *)(r6 + 6) = r1; r1 = *(u8 *)(r6 + 37);

36 \times (u8 *)(r6 + 3) = r1; r1 = *(u8 *)(r6 + 36);

37 \times (u8 *)(r6 + 2) = r1; r1 = *(u8 *)(r6 + 35);

38 \times (u8 *)(r6 + 1) = r1; r1 = *(u8 *)(r6 + 34);

39

*(u8 *)(r6 + 0) = r1; r1 = *(u8 *)(r6 + 39);

40 \times (u8 \times (r6 + 5) = r1; r1 = *(u8 \times (r6 + 38);

41 \times (u8 \times (r6 + 4) = r1; r1 = *(u8 \times (r6 + 41);

|*(u8 *)(r6 + 13) = r1; r1 = *(u8 *)(r6 + 40);

43 *(u8 *)(r6 + 12) = r1; r1 = 1027;

44 * (u32 *) (r6 + 34) = r1; r1 = 18946;

45 \times (u16 \times (r6 + 40) = r1; r3 = r6;

46 \text{ r3} += 34; \text{ r7} = 0;

47 | r1 = 0; r2 = 0;

48 r4 = 92; r5 = 0;

49 call 28;

50 r1 = 1879048261;

51 \times (u32 \times) (r6 + 14) = r1; r1 = 320;

52 \times (u32 *)(r6 + 22) = r1; r1 = *(u32 *)(r6 + 54);

53 \times (u32 \times)(r6 + 30) = r1; r1 = *(u32 \times)(r6 + 58);

54 \times (u32 *)(r6 + 26) = r1; r1 = r0;

55 | r1 >>= 16;

```

```

56 r1 += r0;

57 r1 ^= -1;

|*(u16 *)(r6 + 36) = r1; r3 = r6;

59 r3 += 14; r1 = 0;

60 | r2 = 0; r4 = 20;

61 | r5 = 0;

62 call 28;

63 r1 = r0;

64 r1 >>= 16;

65 r1 += r0;

66 \mathbf{r} \mathbf{1} = -1;

67 * (u16 *) (r6 + 24) = r1; * (u64 *) (r10 - 8) = r7;

68 r2 = r10;

69 r2 += -8; r1 = 0;

70 call 1;

71 if r0 == 0 goto +3 < LBB0-8>;

72 r1 = *(u64 *)(r0 + 0);

73 r1 += 1;

74 \times (u64 \times )(r0 + 0) = r1;

75

76 LBB0_8:

77 | r7 = 3;

78

79 LBB0_9:

80 | r0 = r7; exit;

```

#### While the same code executed with the 4-lane homogeneous architecture is:

```

1 \mid r6 = r1; r7 = 1; r1 = *(u32 *)(r6 + 4); r2 = *(u32 *)(r6 + 0);

2 | r3 = r2;

3 r3 += 14;

4 if r3 > r1 goto +108 <LBB0-9>;

5 | r3 = *(u8 *)(r2 + 12); r4 = *(u8 *)(r2 + 13); r7 = 2;

6 r4 <<= 8;

7 r4 |= r3;

8 if r4 != 8 goto +102 <LBB0_9>;

9 r1 -= r2;

10 r1 <<= 32;

11 r1 s>>= 32; r2 = 601;

12 if r2 s> r1 goto +97 <LBB0-9>;

13 r2 = 98;

14 r2 -= r1; r1 = r6;

15 call 65;

16 r0 <<= 32;

17 r0 >>= 32;

18 if r0 != 0 goto +90 <LBB0_9>;

19 \mathbf{r}1 = \mathbf{r}6; \mathbf{r}2 = 4294967268 11;

20 call 44;

21 r0 <<= 32;

22 | r0 >>= 32; r7 = 1;

23 if r0 != 0 goto +82 <LBB0-9>;

24 r1 = *(u32 *)(r6 + 4); r6 = *(u32 *)(r6 + 0);

25 r2 = r6;

```

```

26 | r2 += 126; r7 = 1;

27 if r2 > r1 goto +76 <LBB0_9>;

28 | r1 = *(u8 *)(r6 + 33);

29 *(u8 *)(r6 + 11) = r1; r1 = *(u8 *)(r6 + 32);

30 \times (u8 \times) (r6 + 10) = r1; r1 = *(u8 \times) (r6 + 31);

31 \times (u8 *)(r6 + 9) = r1; r1 = *(u8 *)(r6 + 30);

32 \times (u8 *) (r6 + 8) = r1; r1 = *(u8 *) (r6 + 29);

*(u8 *)(r6 + 7) = r1; r1 = *(u8 *)(r6 + 28);

33

34 \times (u8 \times (r6 + 6) = r1; r1 = *(u8 \times (r6 + 37);

35 \times (u8 *)(r6 + 3) = r1; r1 = *(u8 *)(r6 + 36);

36 \times (u8 \times )(r6 + 2) = r1; r1 = *(u8 \times )(r6 + 35);

37 \times (u8 *)(r6 + 1) = r1; r1 = *(u8 *)(r6 + 34);

38 \times (u8 *)(r6 + 0) = r1; r1 = *(u8 *)(r6 + 39);

39 *(u8 *)(r6 + 5) = r1; r1 = *(u8 *)(r6 + 38);

40

*(u8 *)(r6 + 4) = r1; r1 = *(u8 *)(r6 + 41);

41

*(u8 *)(r6 + 13) = r1; r1 = *(u8 *)(r6 + 40);

42 * (u8 *) (r6 + 12) = r1; r1 = 1027;

43 \times (u32 \times )(r6 + 34) = r1; r1 = 18946;

44 \times (u16 \times )(r6 + 40) = r1; r3 = r6;

45 r3 += 34; r7 = 0; r1 = 0; r2 = 0;

46 | r4 = 92; r5 = 0;

47

call 28;

48 \ | \ r1 \ = \ 1879048261 \ ;

49 \times (u32 \times) (r6 + 14) = r1; r1 = 320;

50 \times (u32 \times) (r6 + 22) = r1; r1 = *(u32 \times) (r6 + 54);

51 \times (u32 \times) (r6 + 30) = r1; r1 = *(u32 \times) (r6 + 58);

52 \times (u32 \times (r6 + 26) = r1; r1 = r0;

53 r1 >>= 16;

54 r1 += r0;

55

r1 \hat{ } = -1;

56 \times (u16 \times (r6 + 36) = r1; r3 = r6;

57 | \mathbf{r}3 += 14; \mathbf{r}1 = 0; \mathbf{r}2 = 0; \mathbf{r}4 = 20; \mathbf{r}5 = 0;

58 call 28;

59 r1 = r0;

60 r1 >>= 16;

61 r1 += r0;

62 \mathbf{r}1 \hat{} = -1;

63 *(u16 *)(r6 + 24) = r1; *(u64 *)(r10 - 8) = r7; r2 = r10; r1 = 0;

64 r2 += -8;

65 call 1;

66 if r0 == 0 goto +3 <LBB0_8>;

67 | r1 = *(u64 *)(r0 + 0);

68 r1 += 1;

69

*(u64 *)(r0 + 0) = r1;

71 LBB0_8:

72 r7 = 3;

73

74 LBB0_9:

75 | r0 = r7; exit;

```

In this example, when all four lanes are used, they do not require more than two

memory access. This justifies the implementation of a Sephirot core with four lanes, of which 2 of them perform only arithmetic instructions, thus reducing the area occupied. There are a few examples for which this is not true, as is the case of xdp\_redirect\_map. For this particular example, we are going to have a performance-area tradeoff analysis to determine if the two additional MEM units provide a boost in performance such that it will justify the additional area.

In all the XDP examples, only one would benefit from more than four lanes: xdp\_ip\_tunnel.

In the tables below, we report the parallelization analysis made on the XDP subset of examples of eBPF provided in the Linux Kernel documentation.

| Example Name     | # Instructions | # Syllables | Speedup % |

|------------------|----------------|-------------|-----------|

| xdp1             | 38             | 61          | 1.61%     |

| xdp2             | 56             | 77          | 1.375 %   |

| xdp2skb_meta     | 19             | 24          | 1.263 %   |

| xdp_adjust_tail  | 76             | 111         | 1.461 %   |

| xdp_drop_dump    | 10             | 12          | 1.200 %   |

| xdp_fwd          | 167            | 268         | 1.605 %   |

| xdp_monitor      | 101            | 150         | 1.485 %   |

| xdp_redirect     | 16             | 26          | 1.625 %   |

| xdp_redirect_map | 21             | 33          | 1.571 %   |

| xdp_router_ipv4  | 60             | 97          | 1.617 %   |

| xdp_rxq_info     | 61             | 78          | 1.279 %   |

| xdp_sample_pkts  | 23             | 40          | 1.739 %   |

| xdp_sock         | 10             | 17          | 1.700 %   |

| xdp_ip_tunnel    | 190            | 277         | 1.458 %   |

Table 3.4: Speedup with 2 lanes

| 4 Lanes Time %                                            | %00.0   | 8.33%    | 0.00%        | 7.04%           | %00.0         | 5.37%       | 0.00%       | 0.00%        | 5.56%            | %00.0           | 1.96%        | 0.00%           | 0.00%       | 6.83%         |

|-----------------------------------------------------------|---------|----------|--------------|-----------------|---------------|-------------|-------------|--------------|------------------|-----------------|--------------|-----------------|-------------|---------------|

| 2 Lanes Time $\%$   3 Lanes Time $\%$   4 Lanes Time $\%$ | 13.3%   | 5.56%    | 23.0%        | 4.23%           | 11.1%         | 10.7%       | 10.0%       | 21.4%        | 11.1%            | 6.78%           | 7.84%        | 8.33%           | 22.2%       | 4.35%         |

| 2 Lanes Time %                                            | 30.00%  | 38.89%   | 38.46%       | 38.03%          | 11.11%        | 42.95%      | 46.67%      | 28.57%       | 44.44%           | 50.85%          | 31.37%       | 20.00%          | 44.44%      | 42.86%        |

| Speedup %   1 Lane Time %                                 | 26.67%  | 47.22%   | 38.46%       | 50.7%           | 77.78%        | 40.94%      | 43.33%      | 20.00%       | 38.89%           | 42.37%          | 58.82%       | 41.67%          | 33.33%      | 45.96%        |

| Speedup %                                                 | 2.0333% | 2.1388~% | $1.846\ \%$  | 1.563 %         | 1.333 %       | $1.799\ \%$ | $1.667\ \%$ | $1.857\ \%$  | 1.833 %          | 1.644 %         | 1.529~%      | $1.667\ \%$     | $1.889\ \%$ | 1.720 %       |

| # Syllables                                               | 61      | 22       | 24           | 111             | 12            | 268         | 150         | 26           | 33               | 26              | 78           | 40              | 17          | 277           |

| Example Name   # Instructions                             | 30      | 36       | 13           | 71              | 6             | 149         | 06          | 14           | 19               | 59              | 51           | 24              | 6           | 161           |

| Example Name                                              | xdp1    | xdp2     | xdp2skb_meta | xdp_adjust_tail | xdp_drop_dump | pwl-qbx     | xdp_monitor | xdp_redirect | xdp_redirect_map | xdp_router_ipv4 | xdp_rxq_info | xdp_sample_pkts | xdp-sock    | xdp_ip_tunnel |

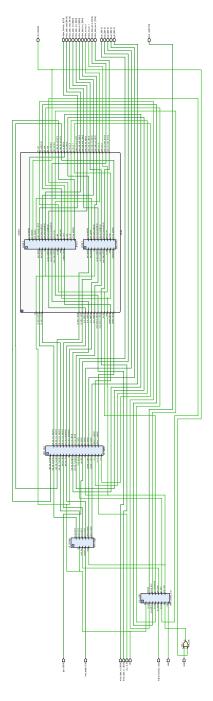

# 3.3.2 2 Lanes Implementation

The Sephirot core has been reduced to only two lanes and synthesized as detailed in the previous chapter. The utilization report is given in **Tab. 3.5**, while the synthesized architecture is depicted in **Fig. 3.11**.

| Resource Type | Used  | Available | Utilization % |

|---------------|-------|-----------|---------------|

| Slice LUTs    | 10280 | 433200    | 2.37%         |

| Slice FFs     | 4114  | 866400    | 0.47%         |

| F7 Muxes      | 533   | 216600    | 0.25%         |

| F8 Muxes      | 260   | 108300    | 0.24%         |

| DSP48E1       | 20    | 3600      | 0.56%         |

Table 3.5: 2-lanes Sephirot Utilization

As we expected from a rule-of-thumb analysis, the area occupied is roughly half of the full Sephirot implemented in the previous chapter. Also, the register file has shrunk by roughly half, as detailed in **Tab. 3.6**.

| Resource Type | Used | Available | Utilization % |

|---------------|------|-----------|---------------|

| Slice LUTs    | 1949 | 433200    | 0.45%         |

| Slice FFs     | 1616 | 866400    | 0.19%         |

| F7 Muxes      | 512  | 216600    | 0.24%         |

| F8 Muxes      | 256  | 108300    | 0.24%         |

Table 3.6: 2-ports Register File Utilization

Figure 3.11: Synthesized 2-lane Sephirot Architecture

#### 3.3.3 4 Lanes - Half Memory Unit Implementation

Considering the xdp\_redirect\_map example, the parallelized code for the 4 lane architecture with 4 memory units is:

```

r2 = *(u32 *)(r1 + 4); r6 = *(u32 *)(r1 + 0); r1 = 0; *(u32 *)(r10 - 4) = r1;

r0 = 1; r1 = r6;

r1 += 14;

if r1 > r2 goto +26 < LBB0_4>;

5 | r2 = r10;

6 r2 += -4; r1 = 0 11;

call 1;

if \quad r0 \ == \ 0 \quad {\tt goto} \ +3 \ < LBB0\_3>;

r1 = *(u64 *)(r0 + 0);

11 *(u64 *)(r0 + 0) = r1;

12

13 LBB0_3:;

14 r1 = *(u16 *)(r6 + 0); r2 = *(u16 *)(r6 + 6);

|*(u16 *)(r6 + 0) = r2; r2 = *(u16 *)(r6 + 8); r3 = *(u16 *)(r6 + 2);

16 \ * (u16 \ *) (r6 \ + \ 8) = r3 \ ; \ * (u16 \ *) (r6 \ + \ 2) = r2 \ ; \ r2 = * (u16 \ *) (r6 \ + \ 10) \ ; \ r3 = * (u16 \ *) (r6 \ + \ 4) \ ; \ r6 + \ 4) \ ; \ r7 = r2 \ ; \ r8 = r8 \ ; \ r8

*(u16 *)(r6 + 10) = r3; *(u16 *)(r6 + 4) = r2; *(u16 *)(r6 + 6) = r1; r1 = 0 11;

17

r2 = 0; r3 = 0;

19

call 51;

20

21 LBB0_4:;

22 exit;

23

r0 = 2; exit;

```

We can thus evaluate the area occupied by a Sephirot implementation in which two of the four lanes are missing the memory unit. The utilization report is depicted in **Tab. 3.7**.

| Resource Type | Used  | Available | Utilization % |

|---------------|-------|-----------|---------------|

| Slice LUTs    | 18843 | 433200    | 4.35%         |

| Slice FFs     | 4487  | 866400    | 0.52%         |

| F7 Muxes      | 1106  | 216600    | 0.51%         |

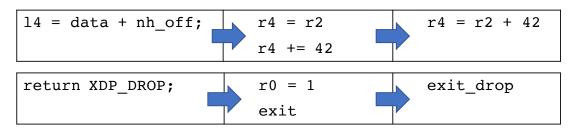

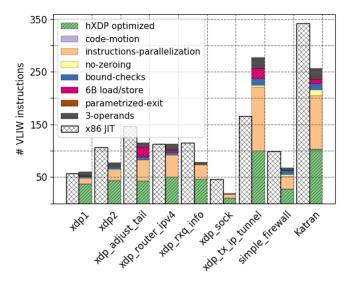

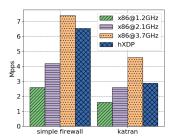

| F8 Muxes      | 512   | 108300    | 0.47%         |